VHDL

¿Qué es un VHDL?

VHDL es un lenguaje de descripción de circuitos electrónicos digitales que utiliza

distintos niveles de abstracción. El significado de las siglas VHDL es (Very High

Speed Integrated Circuits) esto permite acelerar el proceso de diseño.

Los circuitos descritos en VHDL pueden ser simulados utilizando herramientas de

simulación que reproducen el funcionamiento del circuito descrito. Para la realización de la

simulación existe un estándar aprobado por el IEEE.

VHDL por un lado se describirá el aspecto exterior del circuito:

entradas y salidas; y por otro la forma de relacionar las entradas con las salidas.

El aspecto

exterior, cuántos puertos de entrada y salida tenemos, es lo que denominaremos entity. Y la

descripción del comportamiento del circuito architecture, toda architecture tiene que estar

asociada a una entity.

Entity:

Una entidad es la abstracción de un circuito, ya sea desde un complejo sistema

electrónico o una simple puerta lógica, únicamente describe la forma externa del

circuito, en ella se enumeran las entradas y las salidas del diseño y el cual describe las conexiones del

dispositivo hacia el resto del diseño.

- Define externamente al circuito o subcircuito.

- Nombre y número de puertos, tipos de datos de entrada y salida.

- Tienes toda la información necesaria para conectar tu circuito a otros circuitos.

Los puertos pueden ser de entrada (in), salida (out), entrada-salida (inout) o (buffer). Sólo se pueden leer y no se puede modificar su valor internamente en la

descripción del comportamiento del circuito (architecture).

Se presenta un ejemplo de descripción externa del circuito (entity). Sabemos que el circuito presentará dos entradas de tamaño N bits y una

salida de tamaño un bit, particularizamos la entidad para N igual a 8. Como hemos

advertido anteriormente, aunque la función de generic es permitirnos generar un código

más general, una vez que definimos el circuito, tenemos que particularizarlo, por lo que

siempre debe darse un valor a las constantes del campo (generic).

Los pares de entidades y arquitecturas se utilizan para representar la descripción

completa de un diseño.

Una arquitectura describe el funcionamiento de la entidad a la que

hace referencia dentro de architecture tendremos que describir el funcionamiento

de la entidad a la que está asociada utilizando las sentencias y expresiones propias de

VHDL.

- Define internamente el circuito.

- Señales internas, funciones, procedimientos, constantes

- La descripción de la arquitectura puede ser estructural o por comportamiento

- Cada architecture va asociada a una entity y se indica en la primera sentencia.

- Antes de begin se definen todas las variables (señales) internas que vas a necesitar para describir el comportamiento de nuestro circuito.

- Desde begin hasta end escribiremos todas las sentencias propias de VHDL, pero no todas pueden utilizarse en cualquier parte del código.

- El process es una estructura particular de VHD, que se reserva principalmente para contener sentencias que no tengan obligatoriamente definido su valor para todas las entradas (el ejemplo más común es una estructura if-else incompleta).

Identificadores:

En VHDL existen tres clases de objetos por defecto:

Constant: Los objetos de esta clase tienen un valor inicial que es asignado de

forma previa a la simulación y no puede ser modificado durante ésta.

Variable: Contienen un único valor que puede ser cambiado durante la simulación con una sentencia de asignación. Las variables generalmente se utilizan como índices, principalmente en instrucciones de bucle, o para tomar valores que permitan modelar componentes.

Variable: Contienen un único valor que puede ser cambiado durante la simulación con una sentencia de asignación. Las variables generalmente se utilizan como índices, principalmente en instrucciones de bucle, o para tomar valores que permitan modelar componentes.

Las variables NO

representan conexiones o estados de memoria. Pueden ser declaradas antes del

begin de la architecture y/o antes del begin del process, en su declaración se les

puede asignar un valor por defecto.

Signal: Las señales representan elementos de memoria o conexiones y sí pueden

ser sintetizados a cada objeto de nuestro código VHDL que

sea declarado como signal le corresponde un cable o un elemento de memoria

(biestable, registro) en nuestro circuito.

La asignación de una variable a un valor se hace mediante el operador :=

Tienen que ser declaradas antes del begin de la architecture.

Los puertos de una entidad son implícitamente declarados como señales en el

momento de la declaración, ya que estos representan conexiones.

VHDL permite utilizar tipos predefinidos, así

como otros definidos por el usuario. Los tipos predefinidos más comunes son los

siguientes:

La asignación de una señal a un valor se hace mediante el operador <=

bit: Sólo admite los valores 0 y 1, para hacer una asignación a un

objeto tipo bit el valor binario tiene que aparecer entre comas

simples (‘0’ o ‘1’).

bit_vector (rango): El rango, siempre entre paréntesis, indica el número de bits del

vector, estos solo pueden estar formados por ceros y unos.

Para un vector de N bits el rango será N-1 downto 0, donde el

bit más a la izquierda es el más significativo y el bit más a la

derecha el menos significativo (notación binaria estándar).

Para hacer una asignación el valor tiene que aparecer entre

comillas (por ejemplo: “1100”).

boolean: solo admite los valores true y false.

character: cualquier valor ascii.

string: cualquier cadena formada por ascii.

integer rango: cualquier número entero dentro del rango, aquí el rango no va entre paréntesis, puede expresarse como 0 to MAX.

natural rango: cualquier número natural dentro del rango.

positive rango: cualquier número positivo dentro del rango.

real rango: cualquier número real dentro del rango.

std_logic: tipo predefinido en el estándar IEEE 1164,este tipo

representa una lógica multivaluada de 9 valores. Además del

‘0’ lógico y el ‘1’ lógico, posee alta impedancia ‘Z’,

desconocido ‘X’ ó sin inicializar ‘U’ entre otros. Para hacer

una asignación el valor tiene que aparecer entre comas

simples (‘0’, ‘1’, ‘X’, …)

std_logic_vector (rango): representa un vector de elementos std_logic, posee las

mismas reglas de asignación y definición del rango que el tipo

bit_vector pero con un mayor número de valores posibles.

- Para Xilinx ISE todos los puertos de entity tienen que ser obligatoriamente de tipo std_logic o std_logic_vector ya que de esa manera se puede simular un circuito más real.

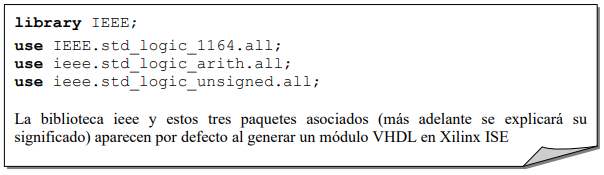

Para poder utilizar el tipo std_logic hay que añadir la librería que lo soporta.

use ieee.std_logic_1164.all

Para poder utilizar las funciones aritmeticológicas definidas (suma, resta

multiplicación).

use ieee.std_logic_arith.all

Si los vectores están en representación binaria pura

use ieee.std_logic_unsigned.all

Los vectores están en C2

use ieee.std_logic_signed.all

Alias: No es un tipo de identificador como tal, es una manera alternativa de

nombrar a un elemento ya existente.

El alias nos ayuda a mejorar la legibilidad del

código que estamos implementando, además puede ayudarnos a simplificar el

manejo del identificador.

alias nombre: tipo is identificador(rango);

Type: En VHDL también se pueden definir tipos como combinación de

identificadores y/o tipos ya existentes. Los más comunes son los siguientes:

Tipo enumerad : Es un tipo de dato con un grupo de posibles valores asignados

por el usuario.

o type nombre is (valor1, valor2, …);

Tipos compuestos: Es un tipo de dato formado con elementos

de otros tipos, existen dos formas de tipos compuestos, arrays

y records.

ARRAY: Es un objeto de datos que consiste en una “colección” de

elementos del mismo tipo.

type nombre is array (rango) of tipo;

La asignación de un valor a una posición del array se realiza

mediante números enteros.

RECORD: Es un objeto de datos que consiste en una “colección” de

elementos de distintos tipos.

type nombre is record

elemento1: tipo_de_dato1;

elemento2: tipo_de_dato2;

end record;

La asignación de un valor a un elemento interno de una señal

definida de tipo record se realiza mediante un punto.

Operaciones: Un operador nos permite construir diferentes tipos de expresiones mediante los

cuales podemos calcular datos utilizando diferentes señales.

En VHDL existen distintos

operadores de asignación con lo que se transfieren y transforman valores de una señal a

otra.

+, -, *, /, mod, rem: operaciones aritméticas.

+, - : cambio de signo.

& : concatenación.

and, or, nand, nor, xor: operaciones lógicas.

:= : asignación de valores a constantes y variables.

<= : asignación de valores a señales.

Comentarios

Publicar un comentario